8 bit nor flash market

The individual flash memory cells exhibit internal characteristics similar to those of the corresponding gates. While EPROMs had to be completely erased before being rewritten, NAND-type flash memory may be written and read in blocks or pages which are generally much smaller than the entire device. One key disadvantage of flash memory is that it can only endure a relatively small number of write cycles in a specific block.

Example applications of both types of flash memory include personal computers, PDAs , digital audio players, digital cameras , mobile phones, synthesizers, video games, scientific instrumentation , industrial robotics , and medical electronics.

In addition to being non-volatile, flash memory offers fast read access times , although not as fast as static RAM or ROM. As of , flash memory costs much less than byte-programmable EEPROM and had become the dominant memory type wherever a system required a significant amount of non-volatile solid-state storage.

Intel Corporation introduced the first commercial NOR type flash chip in This makes it a suitable replacement for older read-only memory ROM chips, which are used to store program code that rarely needs to be updated, such as a computer's BIOS or the firmware of set-top boxes.

Its endurance may be from as little as erase cycles for an on-chip flash memory, [9] to a more typical 10, or , erase cycles, up to 1,, erase cycles. Rather, data must be read on a block-wise basis, with typical block sizes of hundreds to thousands of bits. For example, the microSD card has an area of just over 1.

Flash memory stores information in an array of memory cells made from floating-gate transistors. In single-level cell SLC devices, each cell stores only one bit of information. The floating gate may be conductive typically polysilicon in most kinds of flash memory or non-conductive as in SONOS flash memory. In flash memory, each memory cell resembles a standard metal-oxide-semiconductor field-effect transistor MOSFET except that the transistor has two gates instead of one.

The cells can be seen as an electrical switch in which current flows between two terminals source and drain and is controlled by a floating gate FG and a control gate CG.

On top is the control gate CG , as in other MOS transistors, but below this there is a floating gate FG insulated all around by an oxide layer. Because the FG is electrically isolated by its insulating layer, electrons placed on it are trapped until they are removed by another application of electric field e. Counter-intuitively, placing electrons on the FG sets the transistor to the logical "0" state.

Once the FG is charged, the electrons in it screen partially cancel the electric field from the CG, thus, increasing the threshold voltage V T1 of the cell. This means that now a higher voltage V T2 must be applied to the CG to make the channel conductive.

If the channel conducts at this intermediate voltage, the FG must be uncharged if it was charged, we would not get conduction because the intermediate voltage is less than V T2 , and hence, a logical "1" is stored in the gate. If the channel does not conduct at the intermediate voltage, it indicates that the FG is charged, and hence, a logical "0" is stored in the gate. The presence of a logical "0" or "1" is sensed by determining whether there is current flowing through the transistor when the intermediate voltage is asserted on the CG.

In a multi-level cell device, which stores more than one bit per cell, the amount of current flow is sensed rather than simply its presence or absence , in order to determine more precisely the level of charge on the FG. Despite the need for high programming and erasing voltages, virtually all flash chips today require only a single supply voltage, and produce the high voltages using on-chip charge pumps.

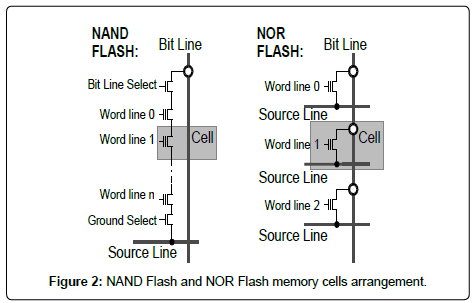

Over half the energy used by a 1. In NOR flash, each cell has one end connected directly to ground, and the other end connected directly to a bit line. NOR flash continues to be the technology of choice for embedded applications requiring a discrete non-volatile memory device.

A single-level NOR flash cell in its default state is logically equivalent to a binary "1" value, because current will flow through the channel under application of an appropriate voltage to the control gate, so that the bitline voltage is pulled down.

To erase a NOR flash cell resetting it to the "1" state , a large voltage of the opposite polarity is applied between the CG and source terminal, pulling the electrons off the FG through quantum tunneling. The erase operation can be performed only on a block-wise basis; all the cells in an erase segment must be erased together. Programming of NOR cells, however, generally can be performed one byte or word at a time.

Compared to NOR flash, replacing single transistors with serial-linked groups adds an extra level of addressing. Bit-level addressing suits bit-serial applications such as hard disk emulation , which access only one bit at a time. Execute-in-place applications, on the other hand, require every bit in a word to be accessed simultaneously. This requires word-level addressing. To read data, first the desired group is selected in the same way that a single transistor is selected from a NOR array.

Next, most of the word lines are pulled up above the V T of a programmed bit, while one of them is pulled up to just over the V T of an erased bit.

The series group will conduct and pull the bit line low if the selected bit has not been programmed. Despite the additional transistors, the reduction in ground wires and bit lines allows a denser layout and greater storage capacity per chip. The ground wires and bit lines are actually much wider than the lines in the diagrams.

Manufacturers try to maximize the amount of usable storage by shrinking the size of the transistors. NAND flash uses tunnel injection for writing and tunnel release for erasing. The vertical layers allow larger areal bit densities without requiring smaller individual cells. V-NAND uses a charge trap flash geometry pioneered in by AMD [ citation needed ] that stores charge on an embedded silicon nitride film. Such a film is more robust against point defects and can be made thicker to hold larger numbers of electrons.

V-NAND wraps a planar charge trap cell into a cylindrical form. The hierarchical structure of NAND Flash starts at a cell level which establishes strings, then pages, blocks, planes and ultimately a die.

A string is a series of connected NAND cells in which the source of one cell is connected to the drain of the next one. Strings are organised into pages which are then organised into blocks in which each string is connected to a separate line called a bitline BL All cells with the same position in the string are connected through the control gates by a wordline WL A plane contains a certain number of blocks that are connected through the same BL.

An individual memory cell is made up of one planar polysilicon layer containing a hole filled by multiple concentric vertical cylinders. The hole's polysilicon surface acts as the gate electrode. The outermost silicon dioxide cylinder acts as the gate dielectric, enclosing a silicon nitride cylinder that stores charge, in turn enclosing a silicon dioxide cylinder as the tunnel dielectric that surrounds a central rod of conducting polysilicon which acts as the conducting channel.

Memory cells in different vertical layers do not interfere with each other, as the charges cannot move vertically through the silicon nitride storage medium, and the electric fields associated with the gates are closely confined within each layer. Growth of a group of V-NAND cells begins with an alternating stack of conducting doped polysilicon layers and insulating silicon dioxide layers.

The next step is to form a cylindrical hole through these layers. Next the hole's inner surface receives multiple coatings, first silicon dioxide, then silicon nitride, then a second layer of silicon dioxide.

Finally, the hole is filled with conducting doped polysilicon. As of , V-NAND flash architecture allows read and write operations twice as fast as conventional NAND and can last up to 10 times as long, while consuming 50 percent less power. They offer comparable physical bit density using nm lithography, but may be able to increase bit density by up to two orders of magnitude. One limitation of flash memory is that, although it can be read or programmed a byte or a word at a time in a random access fashion, it can be erased only a block at a time.

This generally sets all bits in the block to 1. Starting with a freshly erased block, any location within that block can be programmed.

However, once a bit has been set to 0, only by erasing the entire block can it be changed back to 1. A location can, however, be rewritten as long as the new value's 0 bits are a superset of the over-written values.

For example, a nibble value may be erased to , then written as Successive writes to that nibble can change it to , then , and finally Essentially, erasure sets all bits to 1, and programming can only clear bits to 0. File systems designed for flash devices can make use of this capability, for example, to represent sector metadata. Although data structures in flash memory cannot be updated in completely general ways, this allows members to be "removed" by marking them as invalid.

This technique may need to be modified for multi-level cell devices, where one memory cell holds more than one bit. This prevents incremental writing within a block; however, it does help the device from being prematurely worn out by intensive write patterns. This effect is mitigated in some chip firmware or file system drivers by counting the writes and dynamically remapping blocks in order to spread write operations between sectors; this technique is called wear leveling.

Another approach is to perform write verification and remapping to spare sectors in case of write failure, a technique called bad block management BBM.

For portable consumer devices, these wearout management techniques typically extend the life of the flash memory beyond the life of the device itself, and some data loss may be acceptable in these applications. For high reliability data storage, however, it is not advisable to use flash memory that would have to go through a large number of programming cycles. This limitation is meaningless for 'read-only' applications such as thin clients and routers , which are programmed only once or at most a few times during their lifetimes.

This is known as read disturb. The threshold number of reads is generally in the hundreds of thousands of reads between intervening erase operations. If reading continually from one cell, that cell will not fail but rather one of the surrounding cells on a subsequent read.

To avoid the read disturb problem the flash controller will typically count the total number of reads to a block since the last erase. When the count exceeds a target limit, the affected block is copied over to a new block, erased, then released to the block pool.

The original block is as good as new after the erase. If the flash controller does not intervene in time, however, a read disturb error will occur with possible data loss if the errors are too numerous to correct with an error-correcting code. These X-rays can erase programmed bits in a flash chip convert programmed "0" bits into erased "1" bits. Erased bits "1" bits are not affected by X-rays. The low-level interface to flash memory chips differs from those of other memory types such as DRAM , ROM , and EEPROM , which support bit-alterability both zero to one and one to zero and random access via externally accessible address buses.

NOR memory has an external address bus for reading and programming. For NOR memory, reading and programming are random-access, and unlocking and erasing are block-wise. For NAND memory, reading and programming are page-wise, and unlocking and erasing are block-wise. Reading from NOR flash is similar to reading from random-access memory, provided the address and data bus are mapped correctly.

Programming changes bits from a logical one to a zero. Bits that are already zero are left unchanged. Erasure must happen a block at a time, and resets all the bits in the erased block back to one. In older NOR devices not supporting bad block management, the software or device driver controlling the memory chip must correct for blocks that wear out, or the device will cease to work reliably.

The specific commands used to lock, unlock, program, or erase NOR memories differ for each manufacturer. To avoid needing unique driver software for every device made, special Common Flash Memory Interface CFI commands allow the device to identify itself and its critical operating parameters.

Some devices offer read-while-write functionality so that code continues to execute even while a program or erase operation is occurring in the background. Typical NOR flash does not need an error correcting code. NAND flash architecture was introduced by Toshiba in Each block consists of a number of pages. The pages are typically [39] or 2, or 4, bytes in size.

While reading and programming is performed on a page basis, erasure can only be performed on a block basis. NAND devices also require bad block management by the device driver software, or by a separate controller chip. When a logical block is accessed by high-level software, it is mapped to a physical block by the device driver or controller.

A number of blocks on the flash chip may be set aside for storing mapping tables to deal with bad blocks, or the system may simply check each block at power-up to create a bad block map in RAM. The overall memory capacity gradually shrinks as more blocks are marked as bad. When doing erase or program operations, the device can detect blocks that fail to program or erase and mark them bad.

The data is then written to a different, good block, and the bad block map is updated. Most NAND devices are shipped from the factory with some bad blocks. These are typically marked according to a specified bad block marking strategy. By allowing some bad blocks, the manufacturers achieve far higher yields than would be possible if all blocks had to be verified good. When executing software from NAND memories, virtual memory strategies are often used: A memory management unit MMU in the system is helpful, but this can also be accomplished with overlays.

NAND is best suited to systems requiring high capacity data storage. It offers higher densities, larger capacities, and lower cost. It has faster erases, sequential writes, and sequential reads. This allows interoperability between conforming NAND devices from different vendors. The ONFI specification version 1.

Two major flash device manufacturers, Toshiba and Samsung , have chosen to use an interface of their own design known as Toggle Mode and now Toggle V2. This interface isn't pin-to-pin compatible with the ONFI specification. The result is a product designed for one vendor's devices may not be able to use another vendor's devices.

It does not, by itself, prevent NAND cells from being read and programmed individually. Thus random-access reading circuitry was necessary. On the other hand, applications that use flash as a replacement for disk drives do not require word-level write address, which would only add to the complexity and cost unnecessarily.

However, by applying certain algorithms and design paradigms such as wear leveling and memory over-provisioning , the endurance of a storage system can be tuned to serve specific requirements. In practice, flash file systems are used only for memory technology devices MTDs , which are embedded flash memories that do not have a controller. Removable flash memory cards and USB flash drives have built-in controllers to perform wear leveling and error correction so use of a specific flash file system does not add any benefit.

Multiple chips are often arrayed to achieve higher capacities [59] for use in consumer electronic devices such as multimedia players or GPSs. The capacity of flash chips generally follows Moore's Law because they are manufactured with many of the same integrated circuits techniques and equipment. Consumer flash storage devices typically are advertised with usable sizes expressed as a small integer power of two 2, 4, 8, etc.

This includes SSDs marketed as hard drive replacements, in accordance with traditional hard drives , which use decimal prefixes. Most users will have slightly less capacity than this available for their files, due to the space taken by file system metadata. The flash memory chips inside them are sized in strict binary multiples, but the actual total capacity of the chips is not usable at the drive interface. The hierarchical structure of NAND Flash starts at a cell level which establishes strings, then pages, blocks, planes and ultimately a die.

A string is a series of connected NAND cells in which the source of one cell is connected to the drain of the next one. Strings are organised into pages which are then organised into blocks in which each string is connected to a separate line called a bitline BL All cells with the same position in the string are connected through the control gates by a wordline WL A plane contains a certain number of blocks that are connected through the same BL.

An individual memory cell is made up of one planar polysilicon layer containing a hole filled by multiple concentric vertical cylinders. The hole's polysilicon surface acts as the gate electrode. The outermost silicon dioxide cylinder acts as the gate dielectric, enclosing a silicon nitride cylinder that stores charge, in turn enclosing a silicon dioxide cylinder as the tunnel dielectric that surrounds a central rod of conducting polysilicon which acts as the conducting channel.

Memory cells in different vertical layers do not interfere with each other, as the charges cannot move vertically through the silicon nitride storage medium, and the electric fields associated with the gates are closely confined within each layer. Growth of a group of V-NAND cells begins with an alternating stack of conducting doped polysilicon layers and insulating silicon dioxide layers. The next step is to form a cylindrical hole through these layers. Next the hole's inner surface receives multiple coatings, first silicon dioxide, then silicon nitride, then a second layer of silicon dioxide.

Finally, the hole is filled with conducting doped polysilicon. As of , V-NAND flash architecture allows read and write operations twice as fast as conventional NAND and can last up to 10 times as long, while consuming 50 percent less power. They offer comparable physical bit density using nm lithography, but may be able to increase bit density by up to two orders of magnitude.

One limitation of flash memory is that, although it can be read or programmed a byte or a word at a time in a random access fashion, it can be erased only a block at a time. This generally sets all bits in the block to 1. Starting with a freshly erased block, any location within that block can be programmed.

However, once a bit has been set to 0, only by erasing the entire block can it be changed back to 1. A location can, however, be rewritten as long as the new value's 0 bits are a superset of the over-written values. For example, a nibble value may be erased to , then written as Successive writes to that nibble can change it to , then , and finally Essentially, erasure sets all bits to 1, and programming can only clear bits to 0. File systems designed for flash devices can make use of this capability, for example, to represent sector metadata.

Although data structures in flash memory cannot be updated in completely general ways, this allows members to be "removed" by marking them as invalid. This technique may need to be modified for multi-level cell devices, where one memory cell holds more than one bit. This prevents incremental writing within a block; however, it does help the device from being prematurely worn out by intensive write patterns.

This effect is mitigated in some chip firmware or file system drivers by counting the writes and dynamically remapping blocks in order to spread write operations between sectors; this technique is called wear leveling. Another approach is to perform write verification and remapping to spare sectors in case of write failure, a technique called bad block management BBM. For portable consumer devices, these wearout management techniques typically extend the life of the flash memory beyond the life of the device itself, and some data loss may be acceptable in these applications.

For high reliability data storage, however, it is not advisable to use flash memory that would have to go through a large number of programming cycles. This limitation is meaningless for 'read-only' applications such as thin clients and routers , which are programmed only once or at most a few times during their lifetimes.

This is known as read disturb. The threshold number of reads is generally in the hundreds of thousands of reads between intervening erase operations. If reading continually from one cell, that cell will not fail but rather one of the surrounding cells on a subsequent read. To avoid the read disturb problem the flash controller will typically count the total number of reads to a block since the last erase. When the count exceeds a target limit, the affected block is copied over to a new block, erased, then released to the block pool.

The original block is as good as new after the erase. If the flash controller does not intervene in time, however, a read disturb error will occur with possible data loss if the errors are too numerous to correct with an error-correcting code.

These X-rays can erase programmed bits in a flash chip convert programmed "0" bits into erased "1" bits. Erased bits "1" bits are not affected by X-rays. The low-level interface to flash memory chips differs from those of other memory types such as DRAM , ROM , and EEPROM , which support bit-alterability both zero to one and one to zero and random access via externally accessible address buses.

NOR memory has an external address bus for reading and programming. For NOR memory, reading and programming are random-access, and unlocking and erasing are block-wise.

For NAND memory, reading and programming are page-wise, and unlocking and erasing are block-wise. Reading from NOR flash is similar to reading from random-access memory, provided the address and data bus are mapped correctly. Programming changes bits from a logical one to a zero.

Bits that are already zero are left unchanged. Erasure must happen a block at a time, and resets all the bits in the erased block back to one. In older NOR devices not supporting bad block management, the software or device driver controlling the memory chip must correct for blocks that wear out, or the device will cease to work reliably.

The specific commands used to lock, unlock, program, or erase NOR memories differ for each manufacturer. To avoid needing unique driver software for every device made, special Common Flash Memory Interface CFI commands allow the device to identify itself and its critical operating parameters. Some devices offer read-while-write functionality so that code continues to execute even while a program or erase operation is occurring in the background.

Typical NOR flash does not need an error correcting code. NAND flash architecture was introduced by Toshiba in Each block consists of a number of pages. The pages are typically [39] or 2, or 4, bytes in size. While reading and programming is performed on a page basis, erasure can only be performed on a block basis. NAND devices also require bad block management by the device driver software, or by a separate controller chip.

When a logical block is accessed by high-level software, it is mapped to a physical block by the device driver or controller. A number of blocks on the flash chip may be set aside for storing mapping tables to deal with bad blocks, or the system may simply check each block at power-up to create a bad block map in RAM.

The overall memory capacity gradually shrinks as more blocks are marked as bad. When doing erase or program operations, the device can detect blocks that fail to program or erase and mark them bad. The data is then written to a different, good block, and the bad block map is updated. Most NAND devices are shipped from the factory with some bad blocks.

These are typically marked according to a specified bad block marking strategy. By allowing some bad blocks, the manufacturers achieve far higher yields than would be possible if all blocks had to be verified good.

When executing software from NAND memories, virtual memory strategies are often used: A memory management unit MMU in the system is helpful, but this can also be accomplished with overlays. NAND is best suited to systems requiring high capacity data storage.

It offers higher densities, larger capacities, and lower cost. It has faster erases, sequential writes, and sequential reads. This allows interoperability between conforming NAND devices from different vendors. The ONFI specification version 1. Two major flash device manufacturers, Toshiba and Samsung , have chosen to use an interface of their own design known as Toggle Mode and now Toggle V2. This interface isn't pin-to-pin compatible with the ONFI specification.

The result is a product designed for one vendor's devices may not be able to use another vendor's devices. It does not, by itself, prevent NAND cells from being read and programmed individually. Thus random-access reading circuitry was necessary. On the other hand, applications that use flash as a replacement for disk drives do not require word-level write address, which would only add to the complexity and cost unnecessarily. However, by applying certain algorithms and design paradigms such as wear leveling and memory over-provisioning , the endurance of a storage system can be tuned to serve specific requirements.

In practice, flash file systems are used only for memory technology devices MTDs , which are embedded flash memories that do not have a controller. Removable flash memory cards and USB flash drives have built-in controllers to perform wear leveling and error correction so use of a specific flash file system does not add any benefit. Multiple chips are often arrayed to achieve higher capacities [59] for use in consumer electronic devices such as multimedia players or GPSs.

The capacity of flash chips generally follows Moore's Law because they are manufactured with many of the same integrated circuits techniques and equipment. Consumer flash storage devices typically are advertised with usable sizes expressed as a small integer power of two 2, 4, 8, etc.

This includes SSDs marketed as hard drive replacements, in accordance with traditional hard drives , which use decimal prefixes. Most users will have slightly less capacity than this available for their files, due to the space taken by file system metadata. The flash memory chips inside them are sized in strict binary multiples, but the actual total capacity of the chips is not usable at the drive interface. It is considerably larger than the advertised capacity in order to allow for distribution of writes wear leveling , for sparing, for error correction codes , and for other metadata needed by the device's internal firmware.

A joint development at Intel and Micron will allow the production of layer 3. Flash memory devices are typically much faster at reading than writing. Serial flash is a small, low-power flash memory that provides only serial access to the data - rather than addressing individual bytes, the user reads or writes large contiguous groups of bytes in the address space serially.

When incorporated into an embedded system , serial flash requires fewer wires on the PCB than parallel flash memories, since it transmits and receives data one bit at a time.

This may permit a reduction in board space, power consumption, and total system cost. There are several reasons why a serial device, with fewer external pins than a parallel device, can significantly reduce overall cost:. There are two major SPI flash types. The second type has larger sectors. Since the SPI flash lacks an internal SRAM buffer, the complete page must be read out and modified before being written back, making it slow to manage. SPI flash is cheaper than DataFlash and is therefore a good choice when the application is code shadowing.

The two types are not easily exchangeable, since they do not have the same pinout, and the command sets are incompatible. With the increasing speed of modern CPUs, parallel flash devices are often much slower than the memory bus of the computer they are connected to. Because of this, it is often desirable to shadow code stored in flash into RAM; that is, the code is copied from flash into RAM before execution, so that the CPU may access it at full speed.

Once it is decided to read the firmware in as one big block it is common to add compression to allow a smaller flash chip to be used. Typical applications for serial flash include storing firmware for hard drives , Ethernet controllers, DSL modems , wireless network devices , etc. One more recent application for flash memory is as a replacement for hard disks.

Flash memory does not have the mechanical limitations and latencies of hard drives, so a solid-state drive SSD is attractive when considering speed, noise, power consumption, and reliability.

Flash drives are gaining traction as mobile device secondary storage devices; they are also used as substitutes for hard drives in high-performance desktop computers and some servers with RAID and SAN architectures. There remain some aspects of flash-based SSDs that make them unattractive. The cost per gigabyte of flash memory remains significantly higher than that of hard disks. For relational databases or other systems that require ACID transactions, even a modest amount of flash storage can offer vast speedups over arrays of disk drives.

A solid-state drive was offered as an option with the first MacBook Air introduced in , and from onwards, all models shipped with an SSD. Starting in late , as part of Intel 's Ultrabook initiative, an increasing number of ultra-thin laptops are being shipped with SSDs standard.

There are also hybrid techniques such as hybrid drive and ReadyBoost that attempt to combine the advantages of both technologies, using flash as a high-speed non-volatile cache for files on the disk that are often referenced, but rarely modified, such as application and operating system executable files.

As of , there are attempts to use flash memory as the main computer memory, DRAM. Anecdotal evidence [ specify ] suggests that the technology is reasonably robust on the scale of years.

An article from CMU in writes that "Today's flash devices, which do not require flash refresh, have a typical retention age of 1 year at room temperature. The phenomenon can be modeled by Arrhenius law. The heavy competition among the top few manufacturers only adds to the aggressiveness in shrinking the design rule or process technology node.

The decrease in endurance and increase in uncorrectable bit error rates that accompany feature size shrinking can be compensated by improved error correction mechanisms. From Wikipedia, the free encyclopedia. For the neuropsychological concept related to human memory, see flashbulb memory. This section needs additional citations for verification.

Please help improve this article by adding citations to reliable sources. Unsourced material may be challenged and removed. July Learn how and when to remove this template message. Archived from the original on 20 July Archived from the original on 22 April Archived from the original on 3 March Retrieved 18 March Electron Devices Meeting, International.

The designer should weigh the options when using flash memory". Archived from the original on 28 July Retrieved 31 July Retrieved 23 January The flash memory can be reprogrammed up to times.

Archived PDF from the original on 24 September